Ketika Internet of Things dan komputasi awan telah menjadi bagian dari kehidupan, dan media industri sedang berkembang pesat, melalui penggunaan teknologi paling canggih dan desain yang dioptimalkan, komponen elektronik lama tidak menghentikan kemajuannya. Salah satu contohnya adalah konverter analog-ke-digital, yang sekarang dapat mencapai resolusi 32-bit dengan kecepatan melebihi satu megasample per detik (MSPS) dan dengan mudah lulus tes benchmark metrologi tradisional.

Konverter presisi tinggi ini dapat menampilkan resolusi lebih tinggi dari 16 bit, memberikan karakteristik statis dan dinamis yang sebanding, dan digunakan dalam instrumentasi dan sistem akuisisi umum skala besar (pengujian, sertifikasi peralatan), sistem profesional (aplikasi medis dan pencitraan digital spektroskopi), dll. Selain bidang khusus, mereka telah memasuki banyak aplikasi kontrol proses, pengontrol terprogram, kontrol motor skala besar, serta transmisi dan distribusi daya. Saat ini, beberapa arsitektur ADC dapat dibandingkan dalam hal akurasi; sesuai dengan kebutuhan yang berbeda, pilihan spesifik bergantung pada prinsip konversi analog-ke-digital, register aproksimasi berurutan (SAR) dan -. Pada tingkat MSPS, arsitektur ini masing-masing mendukung yang tertinggi Resolusi 24 bit atau lebih adalah 24 bit atau lebih, dan resolusi 32-bit didukung pada kecepatan beberapa ratus kSPS. Ketika dihadapkan dengan resolusi dan tingkat akurasi ini, rentang dinamis berguna yang disediakan oleh konverter ini dapat dengan mudah melampaui penghalang ajaib 100 dBFS (skala penuh). Tantangan nyata bagi pengguna adalah merancang sirkuit pengkondisian analog untuk sinyal yang akan didigitalisasi, dan Ada dua aspek pada desain filter anti-aliasing yang relevan. Dalam dua dekade terakhir, laju pengambilan sampel dan teknologi pemfilteran telah berkembang pesat. Sekarang kami dapat menggabungkan filter analog dan digital untuk mencapai keseimbangan yang lebih baik antara kinerja dan kompleksitas.

Gambar 1 menunjukkan contoh tipikal dari jenis partisi yang cocok untuk sistem akuisisi data. Setelah menyesuaikan sinyal diferensial atau non-diferensial (amplifikasi, penskalaan, adaptasi dan konversi level, dll.), Yang terakhir disaring sebelum dijitasi untuk memenuhi kriteria Nyquist. Menurut tingkat oversampling ADC, penyaringan digital tambahan digunakan untuk memenuhi spesifikasi sistem akuisisi.

Karena meningkatnya permintaan untuk rentang dinamis input ultra lebar, banyak aplikasi yang disebutkan di atas menggunakan ADC resolusi tinggi yang paling canggih. Dengan meningkatnya rentang dinamis, kinerja sistem diharapkan meningkat, rantai regulasi analog akan berkurang, kemacetan, konsumsi energi, dan bahkan biaya material akan menurun.

Oversampling dan manfaatnya

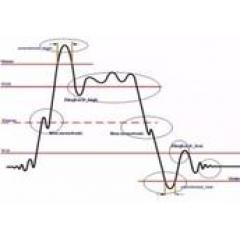

Sebelum munculnya encoder analog-ke-digital resolusi tinggi ultra-cepat, masalah rentang dinamis umumnya diselesaikan dengan metode berikut: menggunakan penguat penguatan yang dapat diprogram cepat, pembanding yang lebih cepat dan / atau paralel beberapa ADC, dan akhirnya menambahkan modul pemrosesan digital yang sesuai, Untuk mewujudkan digitalisasi sinyal yang kuat, bedakan sinyal kecil yang dekat dengan tingkat kebisingan. Dalam arsitektur lama dan sekarang sudah ketinggalan zaman ini, hal itu akan membawa sirkuit kompleks yang sulit dikembangkan, dan dibatasi dalam linieritas, bandwidth, dan frekuensi sampling. Alternatif saat ini adalah menggunakan laju pengambilan sampel yang tinggi dari ADC modern yang lebih ekonomis untuk mencapai tujuan pengambilan sampel yang berlebihan. Dengan mengambil sampel sinyal pada tingkat FSE yang lebih tinggi dari minimum yang disyaratkan oleh teorema Nyquist, operasi penguatan dapat dilakukan dengan memproses dan meningkatkan rasio sinyal-ke-derau dari encoder, sehingga meningkatkan jumlah bit efektif. Nyatanya, derau kuantisasi dan derau termal diasimilasi menjadi derau putih, yang didistribusikan secara seragam ke seluruh pita Nyquist dan seterusnya. Setelah oversampling, pita frekuensi yang berguna dibatasi dengan penyaringan dan ketat pada tingkat sampling minimum yang diperlukan (atau 2 × BW) Setiap kali pita frekuensi dikurangi satu oktaf, energi gangguan akan berkurang 3 dB, seperti yang ditunjukkan pada Gambar 2. Dengan kata lain, faktor oversampling 4 ideal, yang secara teoritis meningkatkan rasio signal-to-noise sebesar 6dB; dengan kata lain, menambahkan satu bit, seperti yang ditunjukkan pada Persamaan 1:

Gambar 1. Rantai sinyal pengukuran umum.

Gambar 2. Perbandingan kepadatan gangguan spektral dengan menambahkan filter desimasi digital.

Singkatnya, oversampling memiliki dua keuntungan, satu adalah dapat meningkatkan rasio signal-to-noise, dan yang lainnya adalah dapat melonggarkan persyaratan untuk filter analog anti-aliasing yang terletak sebelum ADC.

Filter anti-aliasing: dilema partisi

Idealnya, filter terkait ADC, terutama yang bertanggung jawab untuk memecahkan masalah aliasing spektrum, harus memiliki bandwidth respons amplitudo sedatar mungkin dibandingkan keakuratannya, dan atenuasi out-of-bandnya juga harus memenuhi rentang dinamisnya. Klaim. Zona transisi secara umum harus sedalam mungkin. Oleh karena itu, filter low-pass anti-aliasing ini memiliki karakteristik tertentu dan harus mampu menghilangkan gambar parasit, noise, dan suara palsu lainnya. Tergantung pada aplikasinya, perhatian khusus harus diberikan pada respons fase dan perubahan fase yang berlebihan harus dikompensasikan. Meskipun ada banyak rekomendasi yang dianggap sebagai rekomendasi dasar, jika Anda ingin menggabungkan rekomendasi ini dengan persyaratan konverter 24-bit atau 32-bit yang ditentukan, dan kesalahan nonlinier integral dari konverter ini hanya beberapa LSB, ditambah lainnya. Parameter statis dan dinamis serupa, beberapa saran sangat sulit diterapkan.

Seperti disebutkan sebelumnya, oversampling sangat penting di sini karena tidak hanya meningkatkan rasio signal-to-noise, tetapi juga melonggarkan persyaratan untuk spesifikasi filter anti-aliasing analog dan frekuensi cutoff. Seperti yang ditunjukkan pada Gambar 3, distribusi oversampling berada pada pita transisi antara frekuensi cut-off dan awal dari stop band pada kondisi -3 dB.

Gambar 3. Distribusi oversampling adalah pita transisi antara frekuensi cut-off dan awal dari stop band pada kondisi -3 dB.

Teknologi terbaru memungkinkan tingkat konversi SAR ADC presisi tinggi yang telah meningkat secara signifikan dalam beberapa tahun terakhir. Saat ini, tingkat konversi antara 1 MSPS dan 15 MSPS pada resolusi 18-bit. Sebaliknya, kecepatan ADC broadband - dengan resolusi yang sama hampir urutan besarnya lebih rendah, ada masalah penundaan yang luar biasa, dan riak passbandnya terlalu tinggi untuk digunakan dalam sistem akuisisi data, alat ukur lain, dll. aplikasi. Pada dasarnya, akurasi pengukuran keseluruhan menentukan karakteristik yang terakhir, yang terkait dengan parameter statis (dc) dan dinamis (ac). Oleh karena itu, konverter dan rangkaian pengkondisian analog yang menyertai dalam sistem ini harus memenuhi persyaratan teratas dalam spesifikasi. .

Spesifikasi ini mencakup karakteristik umum seperti offset, penguatan, dan kesalahan penyimpangan yang sesuai, kesalahan nonlinier integral (INL) dan diferensial (DNL), serta rasio signal-to-noise (SNR), distorsi harmonik, dan suara palsu (tidak ada rentang dinamis palsu) (SFDR)). SAR ADC memiliki keunggulan kompetitif yang jelas (INL) di beberapa parameter ini serta respons transien, kelebihan input analog, dan penundaan nol, yang memberikan jaminan untuk pengoperasian beberapa sistem input atau pemicu akuisisi dalam mode tunggal.

Sebaliknya, dengan pengecualian LTC2512 dan LTC2500-32, sebagian besar ADC SAR tidak menyertakan filter digital, sehingga operasinya tidak terhalang atau dibatasi oleh beberapa penyaringan low-pass digital yang tak terhindarkan, jika tidak, itu akan menjadi akurasi perhitungan, riak band-pass , Atenuasi stopband supresi, waktu propagasi dan konsumsi daya seimbang. Dalam kebanyakan kasus, pengguna tidak dapat mengontrol nilai koefisien filter internal dari konverter - ini dan harus puas dengannya.

LTC2378-20: ADC SAR 20-bit pertama di pasar

Dalam persaingan untuk kinerja, pada tahun 2014, Linear Technology (sekarang bagian dari ADI) memperkenalkan kepada pelanggan ADC aproksimasi pertama berturut-turut dengan resolusi 20-bit dan linearitas sejati, yang mengalahkan persaingan. Saya tertangkap basah. LTC2378-20 adalah konverter luar biasa yang masih mempertahankan keunggulannya sendiri di semua produk pesaing lainnya yang dekat dengan MSPS.

Mantan teman LTC2378, AD4020 adalah ADC SAR 20-bit pertama ADI yang dapat mendigitalkan sinyal diferensial puncak-ke-puncak 10 V pada 1,8 MSPS. Ini menggabungkan kebisingan rendah, konsumsi daya rendah dan semua fitur LTC2378: kompresi dinamis, sirkuit penjepit, kompensasi transfer muatan, dan mendukung penggunaan amplifier presisi daya rendah (mode impedansi tinggi). Menggunakan catu daya 1,8 V, konsumsi dayanya hanya 15 mW pada 1,8 MSPS. Waktu konversi rekor 350 ns memudahkan untuk memperpanjang waktu akuisisi atau membaca data. Ini dikemas dalam MSOP 10-pin atau QFN 10-pin, yang sama dengan anggota keluarga AD40xx 16-bit hingga 18-bit lainnya. Dalam kisaran suhu 40 ° C hingga 125 ° C, spesifikasi dan pengoperasiannya dijamin sepenuhnya.

Tingkat pengambilan sampel LTC2378-20 dan AD4020 masing-masing adalah 1 MSPS dan 1,8 MSPS, yang membawa kemungkinan signifikan untuk pengambilan sampel yang berlebihan, terutama pada pita frekuensi audio atau pita frekuensi yang lebih tinggi. Untuk alasan ini, filter penghancuran yang disesuaikan harus dipasang di FPGA eksternal atau DSP. Seperti yang disebutkan sebelumnya, yang terakhir dapat dilewati untuk meminimalkan penundaannya jika perlu. Berdasarkan nilai laju pengambilan sampel primer ini, dengan mempertimbangkan pita frekuensi 0 kHz hingga 25 kHz, faktor oversampling yang sesuai adalah sekitar 16 atau 32, dan penguatan pemrosesan adalah 12 dB hingga 18 dB. Pada saat yang sama, secara ketat mengikuti teorema Nyquist, menyederhanakan operasi rutin Filter low-pass anti-aliasing dalam kondisi.

Link ADC ke DSP: semuanya serial

Dalam beberapa tahun terakhir, industri semikonduktor dan lingkaran perancangnya jelas cenderung untuk mengurangi ukuran komponen, membuat pin housing sangat ramping, dan juga menyesuaikan hampir semua input atau output digital serial yang perlu dihubungkan ke bus SPI, port serial sinkron, dll. Masalahnya adalah bahwa konverter ini tidak meninggalkan antarmuka serial untuk pengambilan sampel dan mengontrol berbagai opsi fungsional ADC. Menurut spesifikasinya, antarmuka serial ini kompatibel dengan port serial SPI atau DSP, tetapi tidak demikian. Paling-paling, mereka menyembunyikan register geser yang bertanggung jawab untuk mengatur ritme sinyal clock, digunakan untuk mengekstrak data dari perangkat, atau untuk memasukkan data selama konfigurasi. Seperti semua ADC SAR ini, LTC2378-20 dan AD4020 memerlukan frekuensi serial clock (SCK) untuk memulihkan data dalam unit 20 bit pada laju sampling terukur. Karena fase pembacaan data dibatasi secara ketat pada waktu perolehan (sekitar 300 ns), selama periode konversi, aktivitas digital selama akses eksternal harus dikurangi menjadi benar-benar sunyi; dan laju pengambilan sampel 1 MSPS harus digunakan dalam waktu yang dialokasikan Untuk memulihkan semua bit dari pengambilan sampel, frekuensi clock harus di atas 60MHz. Apakah itu untuk menghasilkan frekuensi clock atau spesifikasi waktu yang akan diterapkan di sisi penerima, ini adalah batasan ketat untuk antarmuka pada pengontrol yang bertanggung jawab untuk mengumpulkan data dari ADC. LTC2378-20 membutuhkan frekuensi sinyal SCK minimum 64 MHz, yang berarti tidak dapat dihubungkan ke mikrokontroler tujuan umum atau DSP yang dilengkapi dengan port serial sinkron (SPORT) dengan frekuensi maksimum sedikit di atas 50 MHz, kecuali untuk beberapa anggota keluarga prosesor Blackfin , Seperti ADSP-BF533 dan ADSP-BF561, kecepatannya bisa mencapai 90 Mbps. Oleh karena itu, beberapa orang khawatir tentang perlunya menggunakan CPLD atau FPGA besar yang dilengkapi dengan rangkaian pembangkit clock jitter rendah. Sebagian besar antarmuka digital ADC SAR keluaran serial memiliki pengaturan waktu dan pola sinyal logika yang kurang lebih sama, seperti yang ditunjukkan pada Gambar 4. Untuk input konfigurasi SDI, selain mode kaskade, juga memiliki persyaratan frekuensi yang jauh lebih rendah. Waktu siklus penuh yang setara dari periode pengambilan sampel ADC adalah (2)

Oleh karena itu, frekuensi pengambilan sampel maksimum ditentukan, dan komposisinya adalah:

(3)

Itu sendiri disesuaikan dengan tingkat pembacaan data keluaran, di mana,

(4) tsck = 1 / Fsck

Gambar 4. Diagram waktu AD4020.

Untungnya, AD4020 memiliki waktu konversi sangat pendek 325 ns, laju pengambilan sampel 1 MSPS, dan waktu pengambilan sampel 675 ns. Berdasarkan ini, frekuensi pembacaan data serial lebih rendah dari 33 MHz dan disinkronkan dengan port serial DSP (seperti SHARC? ADSP-21479) setara, dan konsumsi dayanya juga sangat rendah.

Sistem multi-saluran berdaya sangat rendah

Untuk alasan konsumsi energi, akurasi dan fleksibilitas dalam pemilihan mode operasi, serta pertimbangan komersial, solusi berbasis FPGA tidak dapat dipertimbangkan dalam aplikasi ini. Untuk memproses keluaran serial dari ADC 20-bit ini dan menerapkan filter desimasi optimal, hanya prosesor titik mengambang DSP yang dapat digunakan.

Saat ini, ada banyak sistem akuisisi data yang dapat mengambil sampel secara bersamaan melalui sejumlah besar saluran. Ini menghasilkan banyak ADC yang berjalan secara paralel dan dikontrol oleh pengontrol yang sama, yang juga bertanggung jawab untuk mengumpulkan data dan menyimpannya dalam memori untuk analisis selanjutnya.

Sistem yang dibangun dengan SAR ADC berkinerja tinggi seperti SHARC ADSP-21479 atau versi cepatnya ADSP-21469 dan ADSP-21489 (frekuensi clock 450 MHz) tidak hanya praktis dan layak, tetapi juga dalam hal kinerja, waktu pengembangan, konsumsi energi, dan kekompakan. Ini luar biasa. Prosesor ini memiliki semua fungsi dan periferal yang diperlukan untuk mendukung 8 saluran analog-ke-digital, termasuk antarmuka serial sinkron, pembuatan sinyal jam yang berbeda, dan konversi pemicu. Di antara semua prosesor SHARC, ADSP-21479 adalah satu-satunya DSP floating-point 32/40-bit yang diproduksi dengan proses CMOS 65nm kebocoran rendah. Keuntungannya adalah dapat sangat mengurangi kebocoran atau arus diam, dan suhu sambungannya hampir eksponensial Evolusi level. Arus dinamis, yang merupakan fungsi dari frekuensi dan aktivitas prosesor dan periferalnya, juga lebih rendah daripada prosesor yang diproduksi dalam proses CMOS standar atau cepat. Kekurangannya adalah dibandingkan dengan versi konvensional, frekuensi CPU maksimumnya telah berkurang sekitar 30% -40%, tetapi masih cukup untuk memenuhi kebutuhan aplikasi semacam itu.

ADSP-21479 dilengkapi dengan berbagai periferal, termasuk modul khusus yang disebut Serial Input Port (SIP), yang secara bersamaan dapat menerima aliran sinyal, clock, dan sinyal sinkronisasi dari 8 pemancar serial eksternal yang beroperasi secara sinkron. Faktanya, 8 ADC yang mirip dengan AD4020 dapat langsung dihubungkan ke antarmuka ini, dengan demikian terhubung ke prosesor. Seperti yang ditunjukkan pada Gambar 5, 8 saluran memiliki jam IDP_SCK sendiri, sinkronisasi IDP_FS dan sinyal input IDP_DAT. Setelah dideserialisasi, datanya akan secara otomatis digandakan menjadi memori FIFO 32-bit, 8-kata, dan kemudian meneruskan data DMA 64-bit Operasi membaca yang dilakukan oleh paket atau CPU ditransfer ke RAM internal SHARC. Dalam operasi transmisi DMA, SIP dilayani oleh saluran DMA indeks ganda yang berjalan dalam mode ping-pong otomatis. Selain itu, ADSP-21479 juga dilengkapi dengan empat generator jam presisi (untuk jitter rendah, disingkat PCG), yang dapat menghasilkan jam independen dan pasangan sinyal sinkronisasi dari sumber internal atau eksternal (TCXO). Frekuensi, periode, lebar pulsa, dan fase eksitasi ini dapat diperoleh dengan memprogram pembagi frekuensi internal 20-bit. Setiap unit generasi PCGx menyediakan sepasang sinyal CLK / FS yang dibagikan oleh sepasang konverter AD4020, tetapi jam harus dimatikan selama fase konversi, sehingga gerbang logika diperlukan untuk menggabungkan sinyal IDP_FS dan sinyal IDP_SCK untuk membentuk jam SCK. Diagram waktu pada Gambar 5 menunjukkan bahwa setelah waktu konversi tconv berlalu, 20 bit data harus dibaca dari sampel saat ini pada kecepatan 33,3 MHz secepat mungkin untuk mempertahankan penghalang ajaib 1 MSPS pada frekuensi sampling. Setelah sekitar 600 ns, data ditransfer ke salah satu buffer SIP. Pada saat ini, sinyal IDP_FS atau CNV dapat digunakan untuk memulai siklus konversi baru untuk mengaktifkan AD4020 untuk melakukan operasi konversi baru. Waktu konversi maksimum yang terakhir mencapai 325 ns, yang sesuai dengan lebar pulsa sinyal CNV, yaitu 12 siklus jam IDP_SCK atau 360 ns. Singkatnya, seperti yang ditunjukkan pada diagram waktu pada Gambar 5, siklus pemindaian lengkap memerlukan 32 siklus sinyal IDP_SCK, dan total waktu adalah 960 ns, sehingga laju pengambilan sampel maksimumnya adalah 1.040 MSPS.

Demikian pula, ADC LTC2378-20 dapat dikaitkan dengan ADSP-21489 karena dapat bekerja pada frekuensi clock periferal hingga 50 MHz. Dalam hal ini, laju pengambilan sampel adalah 900 kSPS, seperti yang ditunjukkan pada Tabel 1. Sayangnya, arus suplai diam (Iddint) atau arus bocor yang terakhir jauh lebih tinggi daripada arus dinamis, membuat konsumsi daya total dari konfigurasi ini melebihi daya yang tersedia ke tingkat yang tidak dapat diterima.

Penyaringan penghancuran

Dengan asumsi bahwa konverter ini digunakan dalam mode pengambilan sampel berlebih, perlu untuk menyediakan filter desimasi yang dapat memenuhi persyaratan di atas dan disesuaikan untuk pita frekuensi target guna meminimalkan dampak pada DSP dalam hal daya komputasi dan konsumsi daya yang diperlukan. Saat ini, program yang digunakan untuk mengubah laju pengambilan sampel telah menjadi operasi pemrosesan sinyal digital standar, yang dapat diimplementasikan dengan interpolator dan desimator digital. Dengan mempertimbangkan linearitas respons fase, filter desimasi low-pass mengadopsi topologi respons impuls hingga (FIR), dan topologi yang berbeda dapat digunakan sesuai dengan persyaratan efisiensi:

Filter FIR langsung atau dioptimalkan untuk penghancuran

Filter FIR multi-rate bertingkat (1/2 pita frekuensi)

Filter FIR polifase

Filter polifase tipe FIR dan IIR adalah salah satu implementasi filter desimasi atau interpolasi yang paling efektif. Namun, skema pemrosesan digital tradisional memerlukan penyaringan sebelum penghancuran. Dengan asumsi ini, filter decimation 1 / M terdiri dari filter low-pass diikuti dengan degradasi frekuensi sampling (Gambar 6a). Filter sinyal terlebih dahulu untuk menghindari aliasing spektrum, dan kemudian secara berkala menghilangkan sampel pada tingkat M-1. Namun, penerapan langsung filter decimation ini dengan FIR konvensional atau struktur lain memiliki masalah pemborosan sumber daya, karena sampel yang ditolak adalah hasil dari puluhan atau bahkan ratusan perkalian kumulatif (MAC). Menggunakan filter polifase yang terurai menjadi beberapa bank filter atau filter yang dioptimalkan untuk penghancuran dapat membentuk filter yang efisien berdasarkan karakteristik tertentu (seperti yang ditunjukkan pada Gambar 6b).

Dengan arsitektur SIMD khusus dan akselerator perangkat keras untuk pemfilteran FIR, dan set instruksi yang dioptimalkan untuk pemrosesan sinyal digital, SHARC ADSP-21479 sangat cocok untuk menerapkan jenis filter ini. Setiap unit pemrosesan SHARC memiliki akumulator pengali 32/40-bit, yang dapat melakukan 533 kalkulasi MAC titik tetap atau titik mengambang per detik pada frekuensi CPU 266 MHz. Namun, untuk beberapa aplikasi dengan penundaan yang signifikan (pemerataan ruangan atau efek suara), perlu untuk meningkatkan daya komputasi untuk membebaskan inti dari operasi penggandaan yang intensif dan berkelanjutan seperti pemfilteran FIR, IIR, dan FFT, dan menggunakan akselerator perangkat keras khusus untuk melakukan ini. Operasi. Dengan cara ini, pengguna dapat sepenuhnya memutuskan sendiri untuk menggunakan CPU untuk kalkulasi yang memerlukan algoritme kompleks untuk melakukan pengumpulan yang kompleks. Akselerator khusus filter FIR memiliki memori lokal khusus untuk menyimpan data dan koefisien, dan memiliki karakteristik sebagai berikut:

Gambar 5. Hubungkan 820-bit 1 MSPS SAR ADC ke SHARC DSP melalui deserialisasi; data DMA ditransfer ke RA di dalam DSP

Gambar 6a dan 6b Filter desimasi konvensional dan filter desimasi menggunakan skema polifase.

Mendukung format aritmatika 32-bit fixed-point atau floating-point IEEE-754

Ada empat unit perkalian kumulatif yang berjalan secara paralel

Mendukung mode pemrosesan tingkat tunggal dan banyak tingkat (penghancuran atau interpolasi)

Iterasi sederhana dapat memproses hingga 32 filter FIR, dengan total hingga 1024 koefisien. Kecepatan clock akselerator ADSP-21479 sama dengan kecepatan jam sistem atau perangkat PCLK, yang merupakan setengah dari frekuensi clock CCLK CPU; yaitu 133 MHz. Berdasarkan ini, daya komputasi totalnya adalah 533 MAC / detik. Akselerator tidak memerlukan eksekusi instruksi; operasinya ditentukan oleh konfigurasi register tertentu, dan sepenuhnya bergantung pada transfer DMA untuk memindahkan data antara memori internal dan / atau eksternal.

Tentunya, akselerator dapat melakukan implementasi filter multi-rate (interpolasi atau decimation) dengan cara yang optimal. Karena filter desimasi sederhana hanya memberikan satu hasil keluaran untuk sinyal masukan M, kecepatan keluaran adalah 1 / M kali lebih rendah dari kecepatan masukan. Penerapan filter FIR yang dioptimalkan ini tidak menggunakan bank filter polifase yang kompleks, karena bank filter polifase membutuhkan sejumlah besar penunjuk memori, yang sangat rumit untuk diterapkan; sebaliknya, solusinya hanya menunda keluaran sampel M-1. Hindari melakukan penghitungan ini, dan hanya hitung data yang menghasilkan sampel yang berguna. Ini menghilangkan pemborosan, dan sebagai hasilnya, jumlah operasi dikurangi dengan rasio M-1-dalam contoh ini, 15-sehingga sangat menghemat siklus CPU. Namun, di bawah laju desimasi dan jendela kalkulasi yang begitu singkat, akselerator tidak seefektif inti dengan dua unit kalkulasi, dan saluran DMA diprogram ulang selama transmisi sinyal dari satu filter ke filter lainnya. Akan menimbulkan efek buruk. Jika diimplementasikan dengan unit komputasi dalam mode SISD, biaya jenis filter ini dalam siklus CCLK dapat dinyatakan sebagai:

FIR_Decim_Cycles = N + 2 × M + 19 (5)

N adalah jumlah koefisien filter, dan M adalah laju desimasi.

Biaya implementasi satu iterasi filter decimation ini adalah sekitar 150 siklus dengan kondisi filter FIR (source to assembler 21k), pada rentang frekuensi 0 kHz hingga 24 kHz, spesifikasi riak ± 0,00001 dB, pengambilan sampel pada 62.500 SPS Pada kecepatan, atenuasi out-of-band adalah -130 dB. Filter ini memiliki 97 koefisien (dikuantisasi dalam format 32-bit FP IEEE-754), dan responnya ditunjukkan pada Gambar 7, yang dibuat dengan MATLAB® Filter Designer. Untuk setiap saluran aktif dari SIP atau ADC yang terhubung, respons diulangi dalam instance interupsi DMA pada frekuensi pengambilan sampel.

Gambar 7. Respon filter dari filter decimation.

Untuk beban real-time dan DSP, operasi pemfilteran diulang pada frekuensi 62,5 kSPS, mewakili 9.375.053 siklus CCLK, sedangkan frekuensi pengulangan 8 saluran konversi ADC sedikit lebih dari 8 kali, karena nilai penunjuk memori setiap filter disimpan dalam SHARC Di generator alamat data, Anda dapat dengan cepat menyimpan dan memulihkan. Ini setara dengan 80 juta siklus eksekusi per detik (atau 80 MIPS) untuk SHARC DSP dalam mode SISD. Dalam mode SIMD, karena dua unit pemrosesan berjalan secara paralel, nilainya setengah dari nilai ini. Dalam dua mode yang disebutkan di atas, 8 filter FIR desimator ini menempati ADSP-21479 pada kecepatan 30% dan 15% dan frekuensi clock 266 MHz, masing-masing.

Konsumsi daya

Meskipun konsumsi daya konverter dapat dengan mudah dan akurat dihitung dari spesifikasinya, konsumsi daya prosesor jauh lebih sulit karena rumus perhitungan konsumsi daya prosesor melibatkan banyak parameter, dan kondisi waktu nyata serta mode pengoperasian akan bervariasi. Ini berdampak besar padanya. Meskipun tidak ada penjelasan rinci di sini, pembaca dapat dengan mudah menemukan petunjuk terkait perkiraan konsumsi daya dari setiap komponen prosesor ADSP-214xx dan ADSP-21479 dalam catatan teknis yang relevan, yang mempertimbangkan aktivitas modul fungsional, suhu persimpangan arus diam, dan catu daya. Nilai tegangan, jumlah pin input dan output yang digunakan, berbagai frekuensi eksternal dan beban kapasitif. Menurut deskripsi fungsional pada Gambar 5, untuk beberapa kombinasi DSP dan ADC, konsumsi daya yang sesuai dengan aktivitas DSP dalam jenis aplikasi penyaringan desimasi ini diberikan. Untuk varian DSP terkait ini dengan empat atau delapan ADC, konsumsi daya perlu ditentukan berdasarkan kapasitas fungsional, jumlah input / output, daya komputasi prosesor, dan kinerja ADC secara keseluruhan. Dengan arus diam ultra-rendah, solusi yang dibangun dengan ADSP-21479 dan delapan kluster SAR ADC sebagai intinya tidak hanya solusi dengan konsumsi daya terendah, tetapi juga menyediakan banyak opsi algoritma filter dan fungsi digital lainnya, serta kinerja keseluruhan. Luar biasa.

Contoh sistem akuisisi data multi-saluran (DAQ) ini juga membuktikan bahwa FPGA tidak diperlukan untuk mengimplementasikan tugas pemrosesan sinyal digital. DSP floating-point lebih cocok untuk ADC SAR presisi tinggi, terutama ketika konsumsi daya sangat diperhatikan.

-

- Seperangkat rahasia yang tidak banyak diketahui di bumi; pulau kecil yang akan hilang di Pasifik Selatan, dll.

-

- Resep dan produksi pancake multi-biji-bijian Shandong, yang diwarisi selama seabad! Belajar menghasilkan 8.000 yuan sebulan

-

- Imajinasi mengubah segalanya: tiga hukum termodinamika, E = mc² dan cara perjalanan antarbintang, dll.

-

- Pria yang mengendarai empat mobil ini mungkin tidak lebih sukses, tapi setidaknya manajemen di perusahaan?